|

|

| (5 intermediate revisions by 2 users not shown) |

| Line 1: |

Line 1: |

| − | The system Evariste II is aimed at development and evaluation of cryptographic functions and primitives in reconfigurable hardware (see figure below). It consists of a set of hardware, software and design tools making the development and evaluation of cryptographic functions easier. All the tools are open source and their reliable function was approved in many projects. The hardware components of the toolkit were developed in cooperation with the MICRONIC s.r.o. company, Slovakia. The system is still in development and different interfaces (such as SPI and optical interface) and devices (such as Altera Cyclone V and Microsemi Fusion 2) will be soon available.

| + | <big>'''Evariste III - A Modular Hardware System for Development and Evaluation of Cryptographic Functions and Random Number Generators'''</big> |

| | | | |

| − | [[Image:tools.jpg]]

| |

| − | <br>

| |

| | | | |

| − | The hardware part of the system uses one of five available modules containing one of selected FPGA devices:

| |

| | | | |

| − | * Altera Cyclone III (EP3C25)

| + | The system Evariste III is aimed at development and evaluation of cryptographic functions and primitives in reconfigurable hardware. It consists of a set of hardware, software and design tools making the development and evaluation of cryptographic functions easier. All the tools are open source and their reliable function was approved in many projects. The hardware components of the toolkit were developed in cooperation with the MICRONIC s.r.o. company, Slovakia. The system is still in development and different interfaces (such as SPI and optical interface) and devices (new FPGA Modules) are regularly added to the system. |

| − | * Altera Arria II (EP2AGX45)

| + | |

| − | * Xilinx Spartan 3 (XC3S700AN)

| + | |

| − | * Xilinx Virtex 5 (XC5VLX30T)

| + | |

| − | * Microsemi Fusion (M7AFS600)

| + | |

| | | | |

| − | Besides FPGA device, some modules contain a 4MB SRAM memory with a 32-bit access. All the modules have identical pin-out and can be plugged into the motherboard containing the Cypress EZ USB controller device. In order to reduce the noise in the context of random number generation or side channel attacks, all the modules and motherboards use only linear voltage regulators as FPGA power supplies. The hardware can be called via USB bus using approved original drive from Cypress.

| + | [[Image:02_photos_evaristeIII.png]] |

| | | | |

| − | The reconfigurable hardware design consist of four main parts – IP (intellectual property) functions:

| |

| | | | |

| − | * USB controller interface

| + | The Evariste web site has the following structure: |

| − | * Packet manager

| + | |

| − | * Application controller

| + | |

| − | * Application itself

| + | |

| | | | |

| − | The USB controller interface and the packet manager shouldn’t be modified by the user (their proper operation was already approved in many circumstances). The used should just adapt the application controller to the application needs and he should design his own application IP (for example by using existing examples). | + | * [[Main Page|Main Page]] |

| − | | + | * [[Introduction|Introduction]] |

| − | Both software and hardware interface design tools can take benefit from the use of an equivalent scripting environment using identical commands and syntax. Both the VHDL testbench and the software command interpreter (script.exe) can read the same script file and generate the log file using the same syntax. This makes development of the data interface hardware and software very easy, since the same script can be used in both VHDL testbenches and hardware tests using software calls of hardware functions.<br>

| + | * [[Hardware|The hardware]] |

| − | | + | * [[IP block design|IP block design]] |

| − | Once the hardware functions and their software calls are designed, tested and approved using scripting language commands, the final high-speed software using identical calls of hardware functions can be easily developed. Since both scripting software and application software use the same MS Windows driver, the calls of hardware functions are always perfectly controlled. Several examples of constructing executable files are available.

| + | * [[Software design|Software design]] |

| − | | + | * [[Simulation|VHDL testbench and simulation]] |

| − | The concept of the two scripting environments together with the design of efficient software calls guarantees high flexibility and fast design process, but also very fast data interface in the final software version. Depending on the character of communications (one or two directional), the throughput can attain 40 MB/s (bulk USB mode). When using the optional SRAM memory available on the modules, the sustainable data acquisition rate can be as high as 400 Mbits/s.

| + | * [[File structure|File structure of projects]] |

| | + | * [[Reference designs|Design examples using the Evariste III system]] |

| | + | * [[Downloads|Evariste III Downloads]] |

| | + | * [[Access to hardware|Remote access to Evariste III hardware]] |

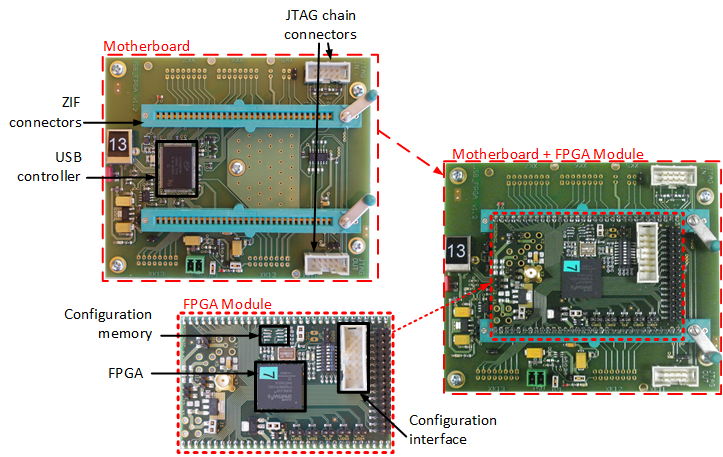

The system Evariste III is aimed at development and evaluation of cryptographic functions and primitives in reconfigurable hardware. It consists of a set of hardware, software and design tools making the development and evaluation of cryptographic functions easier. All the tools are open source and their reliable function was approved in many projects. The hardware components of the toolkit were developed in cooperation with the MICRONIC s.r.o. company, Slovakia. The system is still in development and different interfaces (such as SPI and optical interface) and devices (new FPGA Modules) are regularly added to the system.