Difference between revisions of "Hardware"

(→FPGA modules with a low cost Altera family) |

(→Evariste II FPGA modules) |

||

| (10 intermediate revisions by one user not shown) | |||

| Line 7: | Line 7: | ||

* Actel (Microsemi) Fusion | * Actel (Microsemi) Fusion | ||

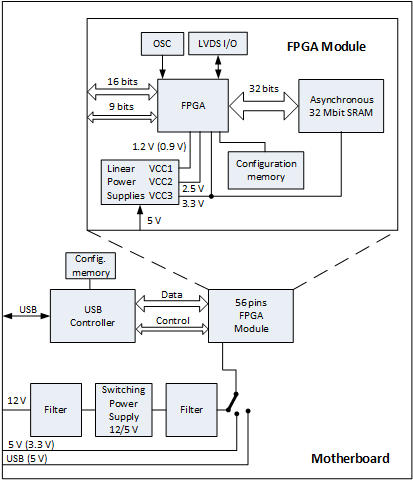

| − | All the modules have the same architecture and topology in order to guarantee a fair comparison of hardware dependent cryptographic functions implemented in different FPGA technologies. Besides the reconfigurable device, each module contains | + | All the modules have the same architecture and topology in order to guarantee a fair comparison of hardware dependent cryptographic functions implemented in different FPGA technologies. Besides the reconfigurable device, each module contains: |

* low noise linear power supply regulators | * low noise linear power supply regulators | ||

* a 4MB SRAM memory with a 32-bit data access | * a 4MB SRAM memory with a 32-bit data access | ||

| Line 15: | Line 15: | ||

The modules featuring FPGA devices with a volatile configuration technology contain also a sufficiently big non volatile configuration memory. All modules contain a proprietary configuration interface and FPGA vendor defined configuration connectors. The modules are plugged into the motherboard, which contains the USB interface hardware controller and power supplies. | The modules featuring FPGA devices with a volatile configuration technology contain also a sufficiently big non volatile configuration memory. All modules contain a proprietary configuration interface and FPGA vendor defined configuration connectors. The modules are plugged into the motherboard, which contains the USB interface hardware controller and power supplies. | ||

| + | [[Image:s_MBoard_v11.jpg|thumb|Evariste II MotherBoard V1.1]] | ||

[[Image:04_hardware_evaristeII.png]] | [[Image:04_hardware_evaristeII.png]] | ||

| Line 27: | Line 28: | ||

All old modules remain to be compatible with the new motherboard (letting 8 pins free), but the new modules can’t fit to the Evariste II motherboard. | All old modules remain to be compatible with the new motherboard (letting 8 pins free), but the new modules can’t fit to the Evariste II motherboard. | ||

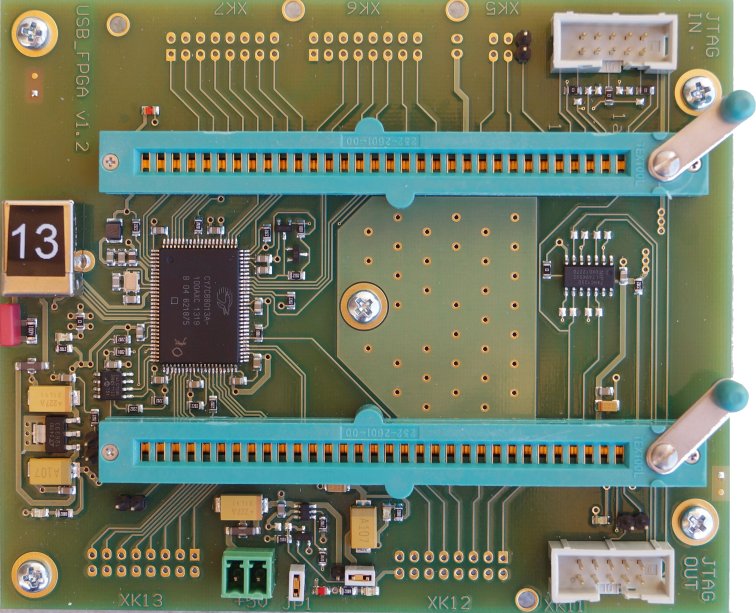

| + | [[Image:carte_mere_v1.2_tiny.jpg|thumb|Evariste III MotherBoard V1.2]] | ||

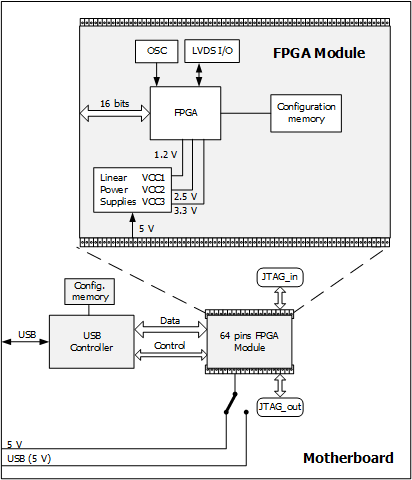

[[Image:04_hardware_evaristeIII.png]] | [[Image:04_hardware_evaristeIII.png]] | ||

| Line 33: | Line 35: | ||

=Motherboard= | =Motherboard= | ||

The Evariste II motherboard features the Cypress EZ USB device CY 7C68013A – 100 ACX and its configuration memory (accessible by the original Cypress software), linear power supplies and high quality low pass ferrite filters. The motherboards can be supplied from a 12 V battery, 5 V external power supply or the USB bus. The motherboard delivers a 5 V power supply to the FPGA module. All kinds of available FPGA modules can be plugged into the motherboard. | The Evariste II motherboard features the Cypress EZ USB device CY 7C68013A – 100 ACX and its configuration memory (accessible by the original Cypress software), linear power supplies and high quality low pass ferrite filters. The motherboards can be supplied from a 12 V battery, 5 V external power supply or the USB bus. The motherboard delivers a 5 V power supply to the FPGA module. All kinds of available FPGA modules can be plugged into the motherboard. | ||

| − | |||

| + | The Evariste III motherboard can be supplied only from an external 5 V power supply or from the USB bus. Two JTAG connectors are added for creating the JTAG chain: JTAG_IN and JTAG_OUT (up to 6 motherboards can be chained on the same JTAG bus for the configuration of FPGAs). A 64 pin ZIF (zero insertion force) connector replaces the 56 pin DIP connector for the daughter module. | ||

=Evariste II FPGA modules= | =Evariste II FPGA modules= | ||

| − | Six hardware modules having the same topology | + | Six hardware modules having the same topology were available with the first version Evariste II. They contain: one FPGA device, FPGA configuration interface and eventually configuration memory (for SRAM-based FPGAs), one 16 MHz quartz oscillator and at least two connectors for LVDS data interface. Most of modules contain also a 4 MB SRAM block (optional) with the 32-bit data interface. |

==FPGA modules with a low cost Altera family== | ==FPGA modules with a low cost Altera family== | ||

| Line 43: | Line 45: | ||

===Low cost Altera Cyclone III module, version 2.2=== | ===Low cost Altera Cyclone III module, version 2.2=== | ||

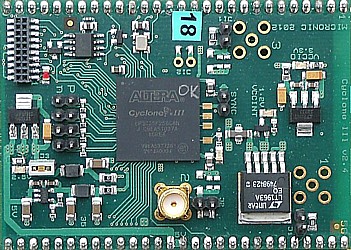

| − | [[Image: | + | [[Image:s_cycl3_v22.jpg|thumb|Cyclone III FPGA module v2.2]] |

The low cost Altera module v. 2.2 features: | The low cost Altera module v. 2.2 features: | ||

* Altera Cyclone III EP3C25F256-C8 FPGA device | * Altera Cyclone III EP3C25F256-C8 FPGA device | ||

| Line 54: | Line 56: | ||

===Low cost Altera Cyclone III module, version 2.4=== | ===Low cost Altera Cyclone III module, version 2.4=== | ||

| − | The second available version of the low cost Altera module (v | + | [[Image:CycloneIIIv24_sm.jpg|thumb|Cyclone III FPGA module v. 2.4]] |

| + | The second available version of the low cost Altera module (v 2.4) features: | ||

* Altera Cyclone III EP3C25F256-C8 FPGA device | * Altera Cyclone III EP3C25F256-C8 FPGA device | ||

* 16-Mbit non volatile serial configuration memory EPCS16 | * 16-Mbit non volatile serial configuration memory EPCS16 | ||

| Line 64: | Line 67: | ||

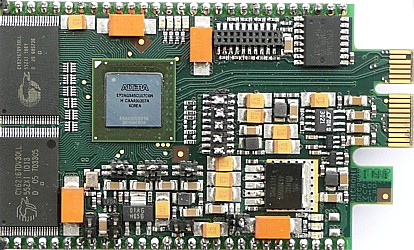

==FPGA module with a high performance Altera family== | ==FPGA module with a high performance Altera family== | ||

| + | [[Image:ArriaIIv10_sm.jpg|thumb|Arria II FPGA module v 1.0]] | ||

The high end Altera module features: | The high end Altera module features: | ||

* Altera Arria II GX EP2AGX45CU17C6 FPGA device | * Altera Arria II GX EP2AGX45CU17C6 FPGA device | ||

| Line 71: | Line 75: | ||

* Linear power supply regulators giving 3.3 V (VCCIO), 2 x 2.5 V (for LVDS and analog parts of PLLs), 1.5 V together with 1.1 V (for transceiver) and 0.9 V (for VCCINT and for digital parts of PLLs). | * Linear power supply regulators giving 3.3 V (VCCIO), 2 x 2.5 V (for LVDS and analog parts of PLLs), 1.5 V together with 1.1 V (for transceiver) and 0.9 V (for VCCINT and for digital parts of PLLs). | ||

| − | [[ | + | [[ArriaII|Module Altera Arria II v1.0 schematics]] |

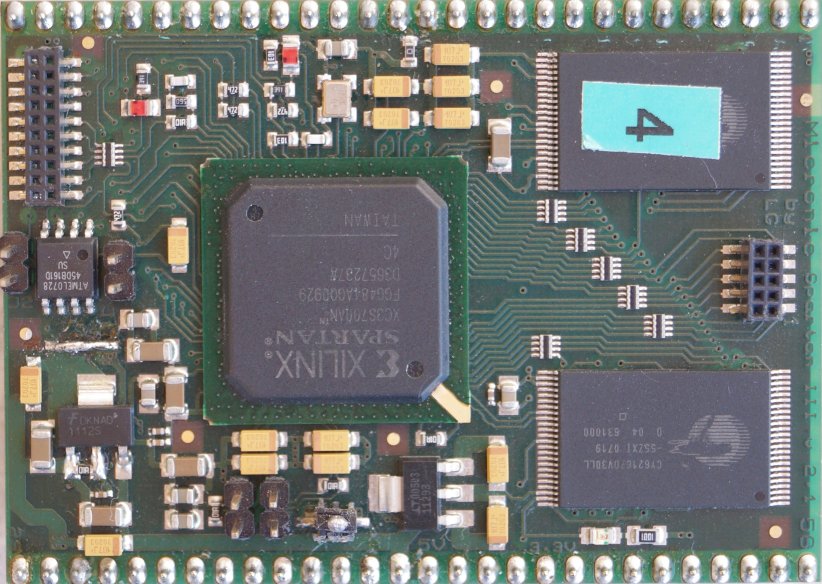

==FPGA module with a low cost Xilinx family== | ==FPGA module with a low cost Xilinx family== | ||

| + | [[Image:s_spartan3.jpg|thumb|Spartan 3 FPGA module v 2.1]] | ||

The low cost Xilinx module v. 2.1 features: | The low cost Xilinx module v. 2.1 features: | ||

* Xilinx Spartan 3 XC3S700AN-FFG484 device | * Xilinx Spartan 3 XC3S700AN-FFG484 device | ||

| Line 84: | Line 89: | ||

==FPGA module with a high performance Xilinx family== | ==FPGA module with a high performance Xilinx family== | ||

| + | [[Image:s_virtex5.jpg|thumb|Virtex 5 FPGA module v 1.0b]] | ||

The high end Xilinx module v 1.0b features: | The high end Xilinx module v 1.0b features: | ||

* Xilinx Virtex 5 XC5VLX30T-FFG323 device | * Xilinx Virtex 5 XC5VLX30T-FFG323 device | ||

| Line 94: | Line 100: | ||

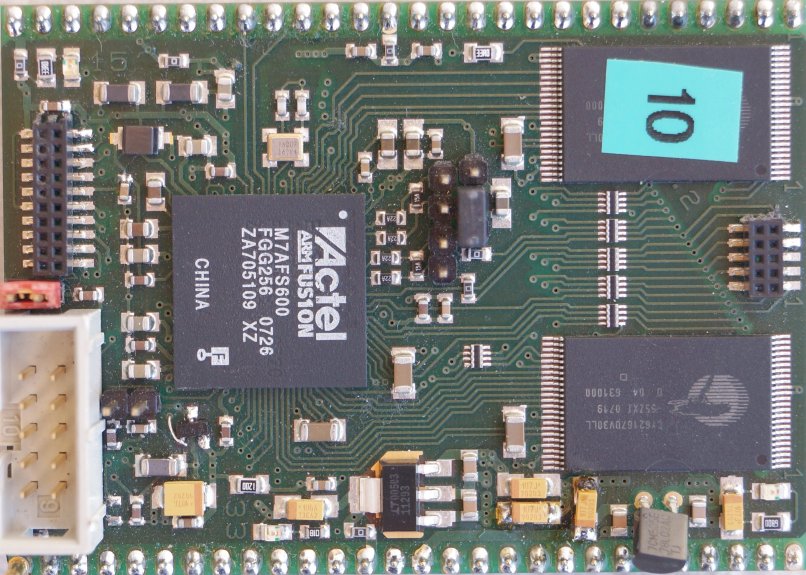

==FPGA module with a non volatile Microsemi technology== | ==FPGA module with a non volatile Microsemi technology== | ||

| + | [[Image:s_fusion.jpg|thumb|Fusion FPGA module v 2.0]] | ||

The Microsemi module v. 2.0 features: | The Microsemi module v. 2.0 features: | ||

* Microsemi Fusion M7AFS600 FGG256X2 device | * Microsemi Fusion M7AFS600 FGG256X2 device | ||

| Line 106: | Line 113: | ||

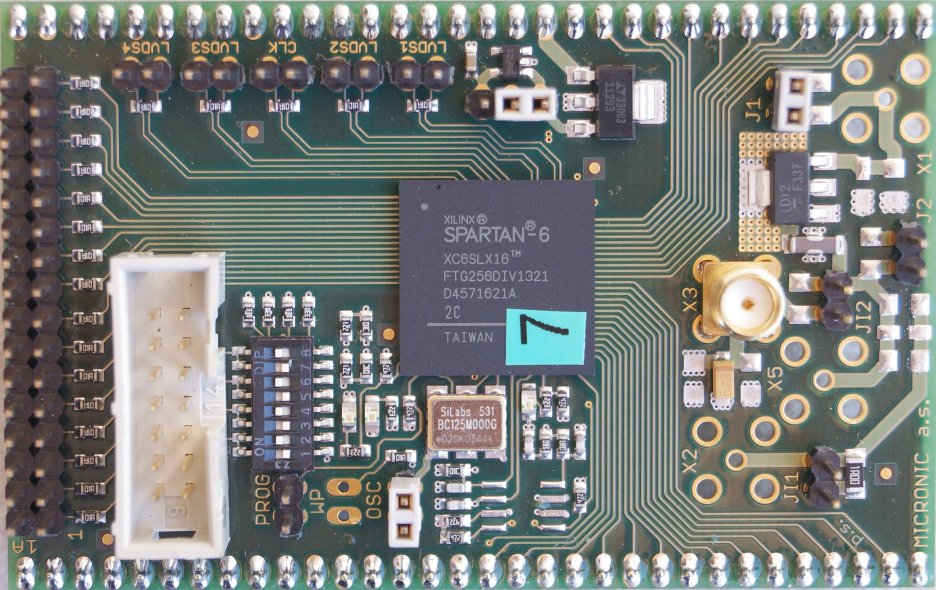

==FPGA modules with a Xilinx Spartan 6 device== | ==FPGA modules with a Xilinx Spartan 6 device== | ||

| + | [[Image:s_spartan6.jpg|thumb|Spartan 6 FPGA module v 1.0]] | ||

The Spartan 6 Xilinx module v.1.0 features: | The Spartan 6 Xilinx module v.1.0 features: | ||

* Xilinx Spartan 6 XC6FLX16-FTG256 device | * Xilinx Spartan 6 XC6FLX16-FTG256 device | ||

| Line 118: | Line 126: | ||

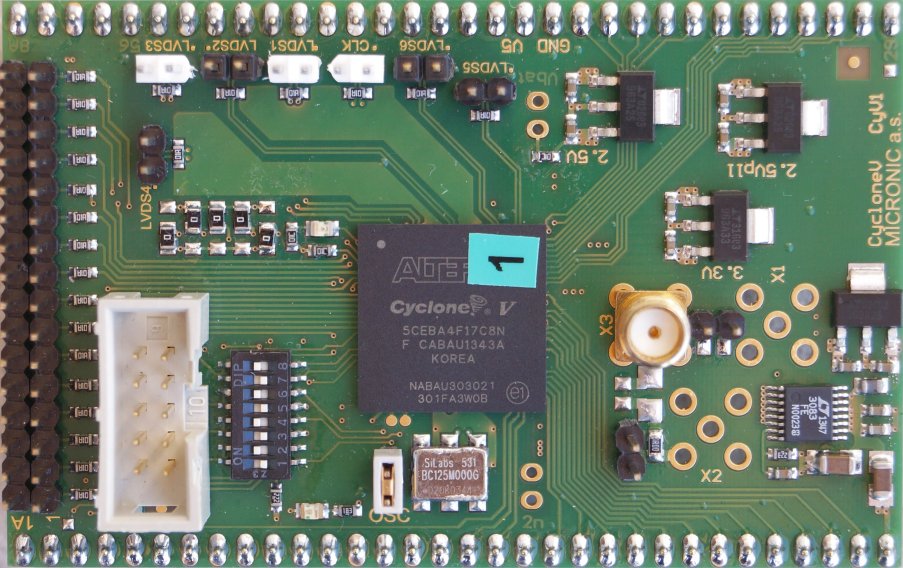

==FPGA modules with an Altera Cyclone V device== | ==FPGA modules with an Altera Cyclone V device== | ||

| + | [[Image:s_cycl5.jpg|thumb|Cyclone V FPGA module v.CyV2]] | ||

The Cyclone V Altera module v.CyV2 features: | The Cyclone V Altera module v.CyV2 features: | ||

* Altera Cyclone V 5CEBA4F17C8N device | * Altera Cyclone V 5CEBA4F17C8N device | ||

| Line 132: | Line 141: | ||

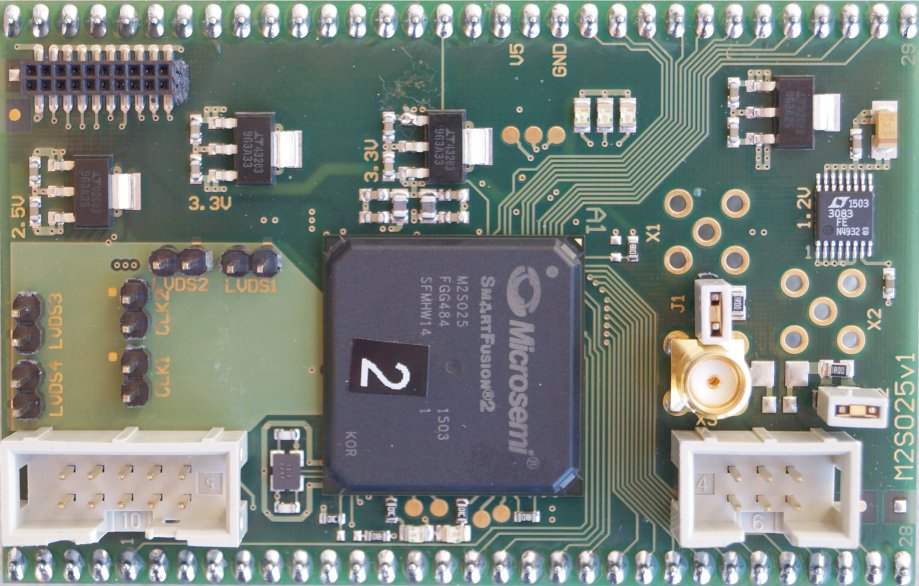

==FPGA modules with a Microsemi SmartFusion 2 device== | ==FPGA modules with a Microsemi SmartFusion 2 device== | ||

| + | [[Image:s_SmartFusion2.jpg|thumb|SmartFusion2 FPGA module v.1]] | ||

The SmartFusion 2 Microsemi module v.1 features: | The SmartFusion 2 Microsemi module v.1 features: | ||

* Microsemi SmartFusion 2 device M2S025FGG484 with embedded Cortex M3 ARM processor | * Microsemi SmartFusion 2 device M2S025FGG484 with embedded Cortex M3 ARM processor | ||

Latest revision as of 11:11, 16 September 2015

The hardware consists of a motherboard (2 versions available, containing power supply and USB controller) on which you can plug one of the nine types of application modules. First version of our system (Evariste II) consists of a motherboard V1.1 with a 56 pin DIP connector on which you can plug one of the six Evariste II modules built around a device from one of the selected FPGA families:

- Altera Cyclone III,

- Altera Arria II,

- Xilinx Spartan 3,

- Xilinx Virtex 5,

- Actel (Microsemi) Fusion

All the modules have the same architecture and topology in order to guarantee a fair comparison of hardware dependent cryptographic functions implemented in different FPGA technologies. Besides the reconfigurable device, each module contains:

- low noise linear power supply regulators

- a 4MB SRAM memory with a 32-bit data access

- a 16 MHz quartz oscillator

- data interface connectors including several LVDS (Low Voltage Differential Signaling) signals.

The modules featuring FPGA devices with a volatile configuration technology contain also a sufficiently big non volatile configuration memory. All modules contain a proprietary configuration interface and FPGA vendor defined configuration connectors. The modules are plugged into the motherboard, which contains the USB interface hardware controller and power supplies.

The new Evariste III system consists of a motherboard V1.2 including:

- a 64 pin ZIF (zero insertion force) connector

- Two JTAG connectors for creating the JTAG chain,

and three new modules:

- Altera Cyclone V

- Xilinx Spartan 6

- Microsemi SmartFusion2

All old modules remain to be compatible with the new motherboard (letting 8 pins free), but the new modules can’t fit to the Evariste II motherboard.

Contents

- 1 Motherboard

- 2 Evariste II FPGA modules

- 3 Evariste III FPGA modules

Motherboard

The Evariste II motherboard features the Cypress EZ USB device CY 7C68013A – 100 ACX and its configuration memory (accessible by the original Cypress software), linear power supplies and high quality low pass ferrite filters. The motherboards can be supplied from a 12 V battery, 5 V external power supply or the USB bus. The motherboard delivers a 5 V power supply to the FPGA module. All kinds of available FPGA modules can be plugged into the motherboard.

The Evariste III motherboard can be supplied only from an external 5 V power supply or from the USB bus. Two JTAG connectors are added for creating the JTAG chain: JTAG_IN and JTAG_OUT (up to 6 motherboards can be chained on the same JTAG bus for the configuration of FPGAs). A 64 pin ZIF (zero insertion force) connector replaces the 56 pin DIP connector for the daughter module.

Evariste II FPGA modules

Six hardware modules having the same topology were available with the first version Evariste II. They contain: one FPGA device, FPGA configuration interface and eventually configuration memory (for SRAM-based FPGAs), one 16 MHz quartz oscillator and at least two connectors for LVDS data interface. Most of modules contain also a 4 MB SRAM block (optional) with the 32-bit data interface.

FPGA modules with a low cost Altera family

Two versions of the low cost Altera module are available: the standard one (version 2.2) has the same structure as FPGA modules for other families (Xilinx and Microsemi) and the second one (version 2.4) is optimized for implementation of side-channel attacks. In this second version of the module, the SRAM memory block is omitted and some filters and connectors for the power trace acquisition are added.

Low cost Altera Cyclone III module, version 2.2

The low cost Altera module v. 2.2 features:

- Altera Cyclone III EP3C25F256-C8 FPGA device

- 16-Mbit non volatile serial configuration memory EPCS16

- 16 MHz quartz oscillator

- Two low power 2MB asynchronous SRAM memories Cypress CY62167DV300LL with 2 x 16-bit data bus

- Linear power supply regulators giving 3.3 V (VCCIO), 2.5 V (for LVDS I/Os and analog part of PLLs) and 2 x 1.2 V (for VCCINT and digital part of PLLs)

Module Altera Cyclone III v2.2 schematics

Low cost Altera Cyclone III module, version 2.4

The second available version of the low cost Altera module (v 2.4) features:

- Altera Cyclone III EP3C25F256-C8 FPGA device

- 16-Mbit non volatile serial configuration memory EPCS16

- 16 MHz quartz oscillator

- Linear power supply regulators giving 3.3 V (VCCIO), 2.5 V (for LVDS I/Os and analog part of PLLs) and 2 x 1.2 V (for VCCINT and digital part of PLLs)

- Set of connectors aimed at implementation of side channel attacks (easy plug-in of differential probes, inclusion of serial resistors, etc.)

Module Altera Cyclone III v2.4 schematics

FPGA module with a high performance Altera family

The high end Altera module features:

- Altera Arria II GX EP2AGX45CU17C6 FPGA device

- 16-Mbit non volatile serial configuration memory EPCS16

- 16 MHz quartz oscillator

- Two low power 2MB asynchronous SRAM memories Cypress CY62167DV300LL with 2 x 16-bit data bus

- Linear power supply regulators giving 3.3 V (VCCIO), 2 x 2.5 V (for LVDS and analog parts of PLLs), 1.5 V together with 1.1 V (for transceiver) and 0.9 V (for VCCINT and for digital parts of PLLs).

Module Altera Arria II v1.0 schematics

FPGA module with a low cost Xilinx family

The low cost Xilinx module v. 2.1 features:

- Xilinx Spartan 3 XC3S700AN-FFG484 device

- 16 MHz quartz oscillator

- FLASH configuration memory AT45DB161D

- Two low power 2MB asynchronous SRAM memories Cypress CY62167DV300LL with 2 x 16-bit data bus

- Linear power supply regulators giving 3.3 V (VCCIO) and 1.2 V (for VCCINT).

Module Xilinx Spartan 3 v2.1 schematics

FPGA module with a high performance Xilinx family

The high end Xilinx module v 1.0b features:

- Xilinx Virtex 5 XC5VLX30T-FFG323 device

- 16-Mbit non volatile FLASH configuration memory AT45DB161D

- 25 MHz quartz oscillator

- Two low power 2MB asynchronous SRAM memories Cypress CY62167DV300LL with 2 x 16-bit data bus

- Linear power supply regulators giving 3.3 V (VCCIO), 3 x 2.5 V (for LVDS I/Os, system monitor and auxiliary circuitry) and 2 x 1.2 V (RocketIO GTP transceivers) and 2 x 1.0 V (VCCINT and RocketIO GTP transceivers)

Module Xilinx Virtex 5 schematics

FPGA module with a non volatile Microsemi technology

The Microsemi module v. 2.0 features:

- Microsemi Fusion M7AFS600 FGG256X2 device

- 16 MHz quartz oscillator

- Two low power 2MB asynchronous SRAM memories Cypress CY62167DV300LL with 2 x 16-bit data bus

- Linear power supply regulators giving 3.3 V (VCCIO, VCCOSC, VCCA, VJTAG and VPUMP) and 2.6 V (LVDS). The 1.5 V is controlled by the internal power supply regulator and an external transistor (the power supply pins VCCINT, VCCPLL and VCC15A).

Module Actel (Microsemi) Fusion schematics

Evariste III FPGA modules

Three new hardware modules having the same topology are available. They contain: one FPGA device, FPGA configuration interface and eventually configuration memory (for SRAM-based FPGAs), connectors for LVDS data interface and few SMA connectors for side channel analysis.

FPGA modules with a Xilinx Spartan 6 device

The Spartan 6 Xilinx module v.1.0 features:

- Xilinx Spartan 6 XC6FLX16-FTG256 device

- 125 MHz quartz oscillator

- FLASH configuration memory AT45DB161E

- four LVDS outputs

- one LVDS specific clock input

- 16 bit single ended general purpose IO bus

- three SMA connectors on the power supply lines.

Module Xilinx Spartan 6 v1.0 schematics

FPGA modules with an Altera Cyclone V device

The Cyclone V Altera module v.CyV2 features:

- Altera Cyclone V 5CEBA4F17C8N device

- 125 MHz quartz oscillator

- a FLASH configuration memory EPCS64SI16N

- four LVDS outputs

- two LVDS general inputs

- two LVDS specific clock inputs

- 16 bit single ended general purpose IO bus

- three SMA connectors on the power supply lines

Module Altera Cyclone V v.CyV2 schematics

FPGA modules with a Microsemi SmartFusion 2 device

The SmartFusion 2 Microsemi module v.1 features:

- Microsemi SmartFusion 2 device M2S025FGG484 with embedded Cortex M3 ARM processor

- 12 MHz quartz oscillator

- 24 MHz clock oscillator

- four LVDS IOs

- two LVDS specific clock inputs

- three SMA connectors on the power supply lines